Looking at the Xilinx Datasheet will notice that the Xilinx FPGA does not have a PLL. In fact, the DCM is the clock management unit.

1. DCM OverviewDCM internal is DLL (Delay Lock Loop structure, the adjustment of the clock offset is formed by a long delay line. DCM parameters have a PHASESHIFT (phase shift), can be changed from 0 to 255. So we can assume There should be 256 delay lines from the input pin clkin to the output pin clk_1x in the internal structure (in fact, since the clock for different frequencies can be changed from 0 to 255, the actual number of delay lines should be larger than this The DCM always compares the input clock clkin with the feedback clock CLKFB. If their delay difference is not equal to the set PHASESHIFT, the DCM will change the number of delay lines between clkin and clk_1x until they are equal. , Output and input form a closed loop, dynamically adjust to the set value and then exit.This time from not equal to equal time is the output clock lock time, after equal, the lock_flag flag will rise.

When DCM finds that the difference between clkin and clkfb is not equal to PHASESHIFT, it adjusts the delay between clk_1x and clkin, so if clk_1x and clkfb are not related, then they can never be locked.

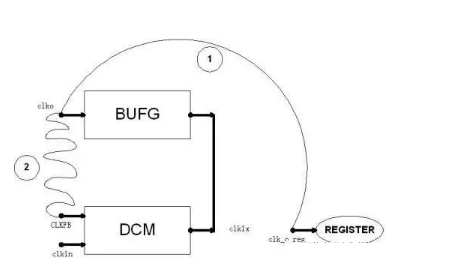

Figure 1. Using DCM and BUFG together

How to use DCMDCM is generally used in conjunction with BUFG. To add BUFG, it should be to enhance the clock's drive capability. The general method of using the DCM is to connect the output clk_1x to the input pin of the BUFG and the output pin of the BUFG back to the feedback clock pin CLKFB of the DCM. In addition, in the FPGA, only the BUFG output pin is connected to the clock network, so in general you can not use DCM, but you will definitely use BUFG. Some brothers always like to drive the internal register directly with the clock input from the outside. In fact, although you did not explicitly instantiate the BUFG at this time, the tool will automatically add it to you.

3. Use DCM to eliminate clock skewUse DCM to eliminate the clock skew. This thing has always been something I hadn't thought about before. The clock starts from the DCM output and goes to the register. The time for this skew is always there. Why can we eliminate it with DCM? It was not until one day suddenly suddenly became clear that they understood the reason. It may be an extremely easy thing for a master, but maybe some friends don't necessarily understand it, so write it out and share it with everyone.

For convenience of explanation, we call the output pin of BUFG as clk_o, and call clk_o_reg when routing the global clock from clk_o to the register, and clkfb when calling from clk_o to the DCM feedback pin CLKFB, as shown in the figure. In fact clk_o, clk_o_reg, and clkfb are all wired together.

The so-called clock skew refers to the delay between clk_o and clk_o_reg. If you open FPGA_Editor and look at the underlying structure, you can see that although DCM and BUFG are close together, they go back from clk_o to clkfb for a long time, resulting in approximately equal delays from clk_o to clk_o_reg and clkfb.

In short, the phases of clk_o_reg and clkfb should be equal. So when the DCM adjusts the phase of clkin and clkfb to be equal, it actually adjusts the clkin and clk_o_reg equal. The phase of clk_1x and clk_o must be preceded by clkin, clkfb, clk_o_reg, and the delay between clk_1x and clk_o is obvious, which is the delay time through that BUFG.

4, further discussion of the clock skewFinally, talk about the concept of clock skew. The clock skew actually refers to the fact that when the clock drives different registers, since the registers may be far apart, the time for the clock to reach different registers may be different. This time difference is called the clock skew. This kind of clock skew can be solved by the clock tree, that is, the clock wiring is formed into a tree structure, so that the distance of the clock to each register is the same. Many FPGA chips have such a clock tree structure. In other words, in this kind of chip, the clock skew basically does not exist.

Having said this, there seems to be a contradiction. Since the problem of clock skew is solved with a clock tree, why do we need DCM+BUFG to solve this problem? In addition, since the clock skew refers to the delay between different registers driven by the clock, can the above mentioned clk_o to clk_o_reg not be called the clock skew?

Let me talk about the latter question first. Inside an FPGA, the clock skew problem has indeed been solved by the FPGA clock solution tree. Under this premise, the clk_o to clk_o_reg can only be called clock delay at best, and cannot be called clock skew. Unfortunately, the design of an FPGA cannot always be done internally. It must exchange data with the outside world. For example, if a 32-bit data is transmitted from the outside and the associated clock is between the data and the on-board clock, the setup hold time relationship (Setup Hold TIme) is met. How do you receive the 32-bit data? If you do not use DCM, connect clkin directly to the input pin of BUFG, then there is a delay between your clk_o_reg and clkin, then your clk_o_reg can maintain the establishment of the data with the incoming data. Relationship? Obviously not. Conversely, if you use DCM and connect the feedback clock, then clk_o_reg and clkin are in phase and you can use it to latch the incoming data. It can be seen that the solution of DCM+BUFG is to solve this problem. And this time delay from clk_o to clk_o_reg, we can see the clock skew between the internal register and the data transmitted from other chips.

From this, we can draw a corollary that when the clock from the crystal oscillator is used as the system clock of the FPGA, we can directly connect to the BUFG without going through the DCM because we do not care about the delay from clkin to clk_o_reg.

DMX Controller

MA Black Horse DMX Controller lighting console

Technical Parameter

1.Intel core 3 generation processor Inter(R) core (TM) i5-3380M CPU

2. 120 GB solid state disk, 8 GB memory, corn I5 motherboard

3.standard 6 DMX output ports and MIDI interfaces, 3072 DMX channels

4. Built-in two 19-inch high-definition touch screens

5.21 program playback putter, 42 program storage function keys

6. 1 main control dimming wheel, 4 attribute coding wheel

7. 1 mian control putter, 2 AB putter

8 Hydraulic screen Angle adjustment support structure

9.size: 82*680*130mm, G, weight: about 56KG with flycase

Our company have 13 years experience of LED Display and Stage Lights , our company mainly produce Indoor Rental LED Display, Outdoor Rental LED Display, Transparent LED Display,Indoor Fixed Indoor LED Display, Outdoor Fixed LED Display, Poster LED Display , Dance LED Display ... In additional, we also produce stage lights, such as beam lights Series, moving head lights Series, LED Par Light Series and

Controller Series,DMX Controller,Console,DMX Console

Guangzhou Chengwen Photoelectric Technology co.,ltd , https://www.cwstagelight.com