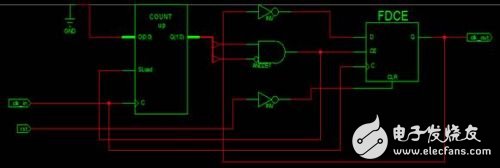

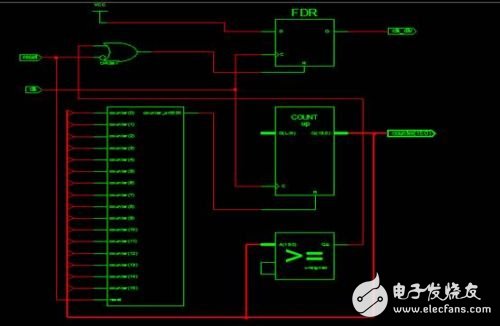

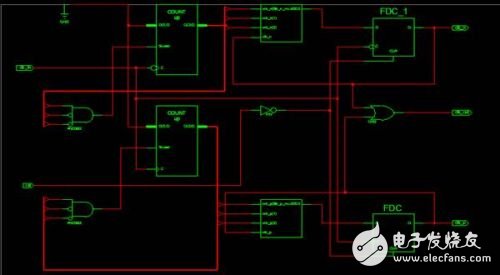

Original from: The frequency divider is an electronic circuit that makes the output signal frequency one of the integer fractions of the input signal frequency. In many electronic devices, such as electronic clocks, frequency synthesizers, etc., signals of different frequencies are required to work together. The commonly used method is to use a crystal oscillator with high stability as the main vibration source, and obtain various frequencies required by conversion. Ingredients, frequency dividers are a major means of transformation. Most of the early crossovers were sinusoidal dividers. With the development of digital integrated circuits, pulse dividers (also known as digital dividers) have gradually replaced sinusoidal dividers. The following is a 50% duty cycle divider based on the Verilog HDL language. 1 Even frequency division evenly is relatively simple. If it is divided by N, it only needs to count to N/2-1, then the clock is flipped and the count is cleared. In this cycle, the N (even) frequency can be obtained. code show as below. Module fp_even(clk_out,clk_in,rst);output clk_out;input clk_in;input rst;reg [1:0] cnt;reg clk_out;parameter N=6; always @ (posedge clk_in or negedge rst) beginif(!rst) begin Cnt <= 0; clk_out <= 0; endelse begin if(cnt==N/2-1) begin clk_out <= !clk_out; cnt<=0; end else cnt <= cnt + 1; endendendmodule can be changed by changing the parameter N The value of the bit and the bit width of the count variable cnt achieve any even division. RTL schematic with even frequency (N=6):

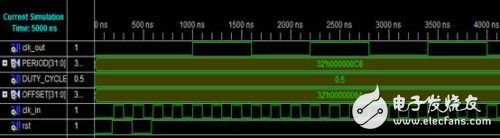

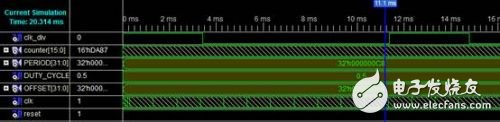

Behavioral simulation results of even frequency (N=6):

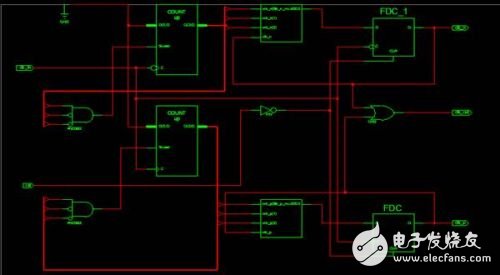

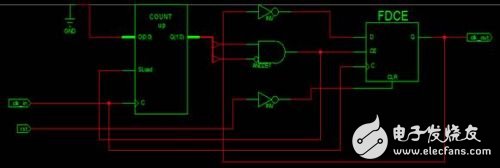

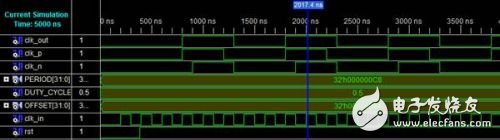

2 Odd frequency is divided into odd (N) frequency division, which is counted to (N-1)/2 with rising edge and counted again to N-1; counted to (N-1)/2 with falling edge, and then counted to N -1, get two waveforms, and then phase them to get a divide by N. Code is as follows: module fp_odd (clk_out, clk_p, clk_n, clk_in, rst); output clk_out; output clk_p, clk_n; input clk_in, rst; reg [2: 0] cnt_p, cnt_n; reg clk_p, clk_n; parameter N = 5; Always @ (posedge clk_in or negedge rst) begin if(!rst) cnt_p <= 0; else if(cnt_p==N-1) cnt_p <=0; else cnt_p <= cnt_p + 1; end always @ (posedge clk_in or negedge rst) begin if (! rst) clk_p <= 0; else if (cnt_p == (N-1) / 2) clk_p <= clk_p;! else if (cnt_p == N-1) clk_p <= clk_p!; End always @ (negedge clk_in or negedge rst) begin if(!rst) cnt_n <= 0; else if(cnt_n==N-1) cnt_n <=0; else cnt_n <= cnt_n + 1; end always @ (negedge clk_in Or negedge rst)begin if(!rst) clk_n <= 0; else if(cnt_n==(N-1)/2) clk_n <= !clk_n; else if(cnt_n==N-1) clk_n <= !clk_n ;end assign clk_out = clk_p | clk_n;endmodule

RTL SchemaTIc:

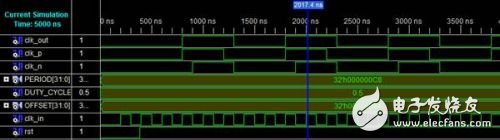

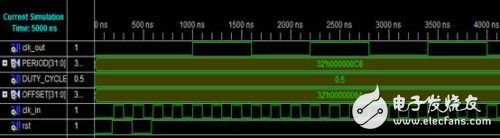

Simulate Behavioral Model:

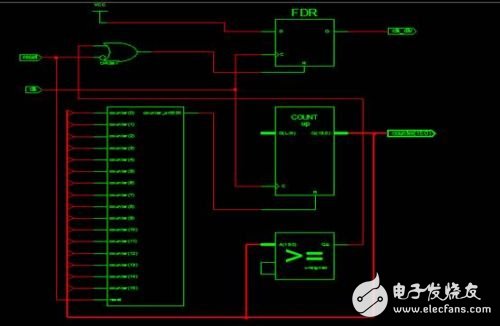

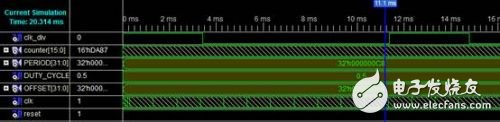

Similarly, any odd frequency division can be realized by changing the value of the parameter N and the bit widths of the count variables cnt_p and cnt_n. 3 Arbitrary frequency division of any duty cycle In the verilog program design, we often have to divide a frequency arbitrarily, and the duty cycle also has certain requirements. If there is a certain requirement for the program, now in the first two experiments On the basis of a simple summary, achieve an arbitrary division of any duty cycle for a frequency. For example: The FPGA system clock is 50M Hz, and the frequency we want to generate is 880Hz, then we need to divide the system clock. It is easy to think of dividing by frequency /880 = 56818. Obviously this number is not the power of 2, then we can set a parameter, let it re-count when it is 56818 can be achieved. Procedure is as follows: module div (clk, clk_div); input clk; output clk_div; reg [15: 0] counter; always @ (posedge clk) if (counter == 56817) counter <= 0; else counter <= counter + 1 ;sign clk_div = counter[15]; The application of the endmodule crossover is very wide. The general practice is to use the high frequency clock to count, and then use the output of the counter as the working clock for other logic design. The above program is a reflect. Let's take a look at its duty cycle: we clearly know that this output waveform is low when the counter is 0 to 32767, high when 32768 to 56818, and the duty cycle is 40% more if we To achieve a duty cycle of 50%, then we need to set a parameter to make it half of the 56,617, so that when the waveform is flipped, it can achieve the result. Procedure is as follows: module div (clk, clk_div); input clk; output clk_div; reg [14: 0] counter; always @ (posedge clk) if (counter == 28408) counter <= 0; else counter <= counter + 1 ; reg clk_div; always @ (posedge clk) if (counter == 28408) clk_div <= ~ clk_div; endmodule continue any let us look at how to implement the duty cycle, such as is generated by the frequency divider 50 M 880Hz, and the frequency-divided to give The duty cycle of the signal is 30%. 56818 & TImes; 30% = 17045module div (clk, reset, clk_div, counter); input clk, reset; output clk_div; output [15: 0] counter; reg [15: 0] counter; reg clk_div; always @ (posedge clk) If(!reset) counter <= 0;else if(counter==56817) counter <= 0;else counter <= counter+1;always @(posedge clk)if(!reset) clk_div <= 0;else if( Counter<17045) clk_div <= 1;else clk_div <= 0;endmoduleRTL level description:

Simulation results:

4 Summary Through the comparison of the above examples, it is not difficult to find that the method of realizing any frequency division of any point-to-space ratio by means of a counter is simple, and the code is simple, easy to understand and universal when using the verilog language for behavior description. Through the above study, the crossover has a deeper understanding and will be widely used in future studies.

Copper Lugs

Copper Lugs,Copper Cable Lugs,Plating Copper Cable Lugs,Copper Tube Terminal Lugs

Taixing Longyi Terminals Co.,Ltd. , https://www.txlyterminals.com